What Happens to PCIe Signals Traversing Blind Vias at Higher Speeds? | Lee Ritchey's Classroom | Altium

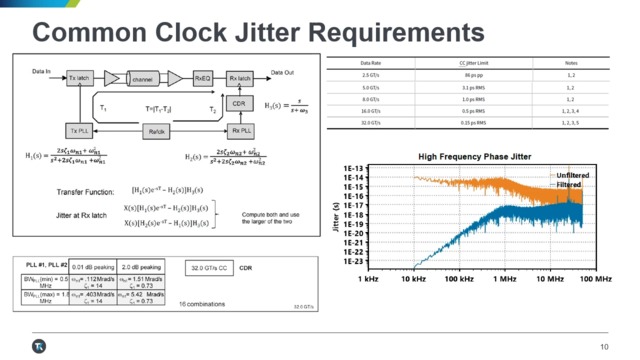

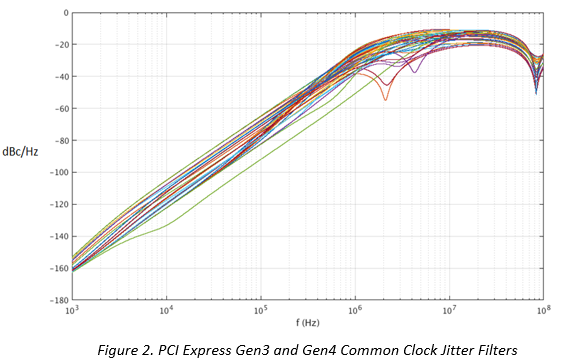

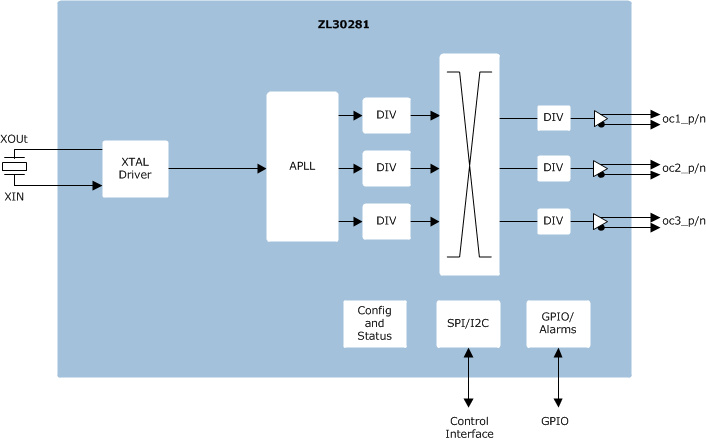

Timing is Everything: How to optimize clock distribution in PCIe applications - Analog - Technical articles - TI E2E support forums

Timing is Everything: How to optimize clock distribution in PCIe applications - Analog - Technical articles - TI E2E support forums

.jpg)